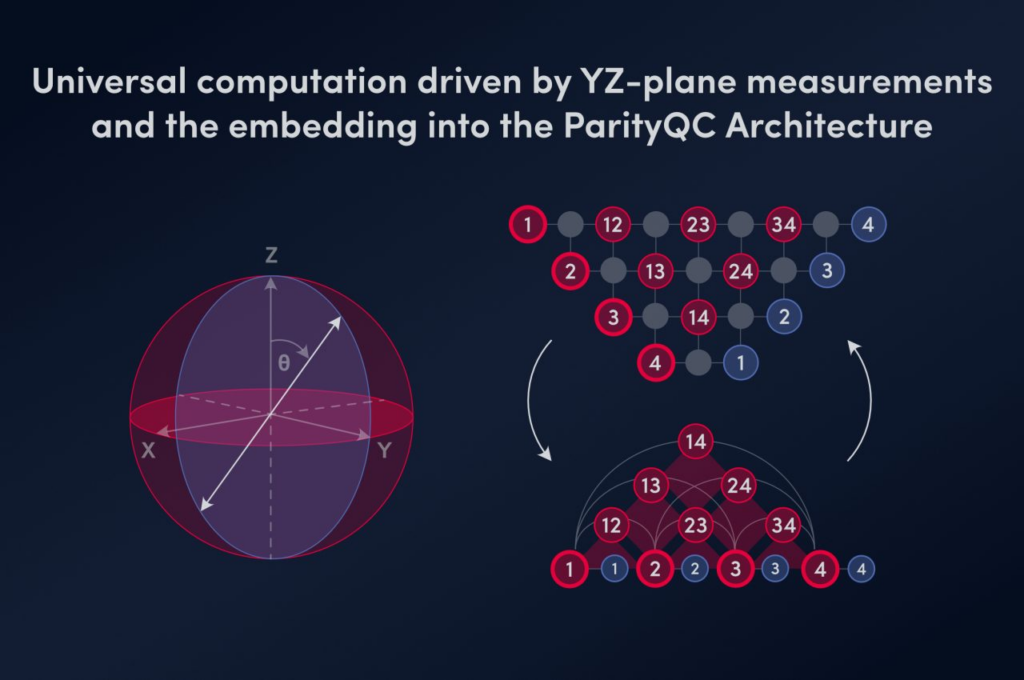

Physicists at ParityQC have established that universal measurement-based quantum computing (MBQC) is possible using single-qubit measurements restricted entirely to the YZ-plane of the Bloch sphere. This research, published in the preprint “YZ-plane measurement-based quantum computation: Universality and Parity Architecture implementation,” completes the scientific investigation into the universality of the three principal planes (XY, XZ, and YZ). By proving that YZ-plane measurements are computationally sufficient, the team has unified previously separate threads of research and provided a new pathway for executing algorithms on highly restricted hardware sets.

In the MBQC paradigm, computation is driven by a prescribed sequence of measurements on a large entangled state—a “measurement pattern”—rather than standard gate sequences. The ParityQC team demonstrated that while YZ-plane patterns following “uniform determinism” are too restrictive for universality, a more relaxed notion of determinism allows for the design of a fully universal pattern. This discovery is technically significant because YZ-plane measurements are often experimentally more convenient to implement on specific physical layers, potentially reducing the complexity of the control stack while maintaining the ability to execute any quantum algorithm.

Integration with the ParityQC Architecture

A primary outcome of this research is the direct embedding of YZ-plane measurement patterns into the ParityQC Architecture. The architecture’s bipartite structure, which separates data qubits and parity qubits, aligns with the graph-state requirements for YZ-plane MBQC. Key features of this implementation include:

- Elimination of Long-Range Interactions: The patterns can be embedded into graphs featuring only local interactions, making them amenable for current hardware platforms that struggle with the high error rates of long-distance connectivity.

- ParityQC Twine Compatibility: This work marks the introduction of ParityQC’s compilation and architectural concepts—previously used for annealing and gate-based systems—into the MBQC realm.

- Hardware Efficiency: By restricting measurements to a single plane, the demands on the physical layer are minimized, allowing hardware optimized for the ParityQC Architecture to support universal computation with reduced calibration overhead.

You can find the official announcement regarding ParityQC’s YZ-plane universality research here and access the preprint of the study on arXiv here.

May 5, 2026