Riverlane, a developer of quantum error correction (QEC) technology, has released performance metrics for its second-generation Deltaflow 2 system, demonstrating a mean latency of 16.32µs. This result was achieved using data from Google’s 2024 “Willow” experiment, which involved a distance-5 (d5) rotated surface code quantum memory test over one million rounds. The demonstrated latency is approximately four times lower than the 63µs reported in the original Google study. Furthermore, Riverlane reported that its maximum sub-shot latency—the time to process individual data windows—outperformed the previously published benchmarks by a factor of ten.

Low latency is a critical requirement for real-time QEC because it determines the logical clock speed of a quantum computer. In operations such as magic state teleportation, a logical gate can only be executed after an error-corrected measurement result is issued. If this latency (τ) is too high, the execution of non-Clifford gates becomes impossible, stalling the progression toward universal fault-tolerant computing. Riverlane’s current results move the platform closer to the industry-recognized 10µs threshold required for utility-scale applications, such as factoring 2048-bit RSA integers.

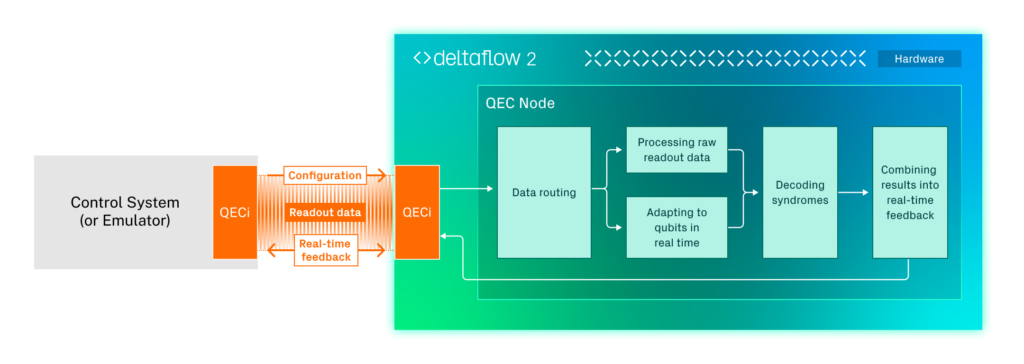

The Deltaflow 2 architecture achieves these speeds through a hardware-centric approach utilizing Field Programmable Gate Arrays (FPGAs). Key features include a proprietary Local Clustering Decoder (LCD), which is designed to decode syndromes in under 1µs per round. To manage the massive data throughput generated by a Quantum Processing Unit (QPU), the system employs a streaming windowing scheme. This allows the decoding graph to be processed continuously in “chunks” rather than waiting for an entire computational shot to conclude, preventing data backlogs during long-running experiments.

A central component of the Deltaflow ecosystem is the Quantum Error Correction interface (QECi). In contrast to general-purpose data movement platforms like NVIDIA’s NVLink, QECi is a purpose-built, open-source specification designed specifically for QEC. While NVLink provides a generic transport layer between GPUs and control systems, QECi defines both the physical interface and the specific data formatting required for real-time error interpretation. Riverlane notes that while ROCE-based physical interfaces (common in GPUs) may encounter bottlenecks as systems scale beyond 300 physical qubits, QECi is engineered to maintain a round-trip latency of under 400ns.

The reported metrics mark the completion of the “Quantum Memory” phase (Phase 1) of Riverlane’s multi-year QEC roadmap. The upcoming Deltaflow 3, scheduled for release later in 2026, is intended to transition from simple quantum memory to active logical operations. This next phase will focus on implementing lattice surgery to perform error-corrected logical gates efficiently and achieving higher error suppression rates. The ultimate goal of the roadmap is to reach the “TeraQuOp” scale by 2033, enabling quantum systems to perform a trillion reliable logical operations.

By validating real-time QEC on continuous data from a high-performance QPU, Riverlane aims to demonstrate a viable path to utility-scale systems. The company emphasizes that while Google’s original experiment was not primarily focused on optimizing decoder latency, these new benchmarks provide a standard for system-level response times. As hardware qubit types become faster, the ability of the decoding stack to keep pace with readout rates remains a primary engineering challenge for the development of fault-tolerant quantum computers.

For the full technical breakdown of the Deltaflow 2 performance metrics and the comparison to Google’s 2024 results, consult the official Riverlane blog here. Detailed information on the QECi specification and the Riverlane Technology Roadmap can be found on the company’s website here.

April 9, 2026