Riverlane has announced the peer-reviewed publication of its Local Clustering Decoder (LCD) paper in Nature Communications, demonstrating a hardware-integrated solution for real-time quantum error correction (QEC). The LCD is the first hardware decoder chip to simultaneously deliver real-time speed (under 1 μs per round), high accuracy, and adaptive performance. This concurrent achievement is critical for the “backlog problem,” where error data (syndromes) otherwise accumulate faster than a classical controller can process them.

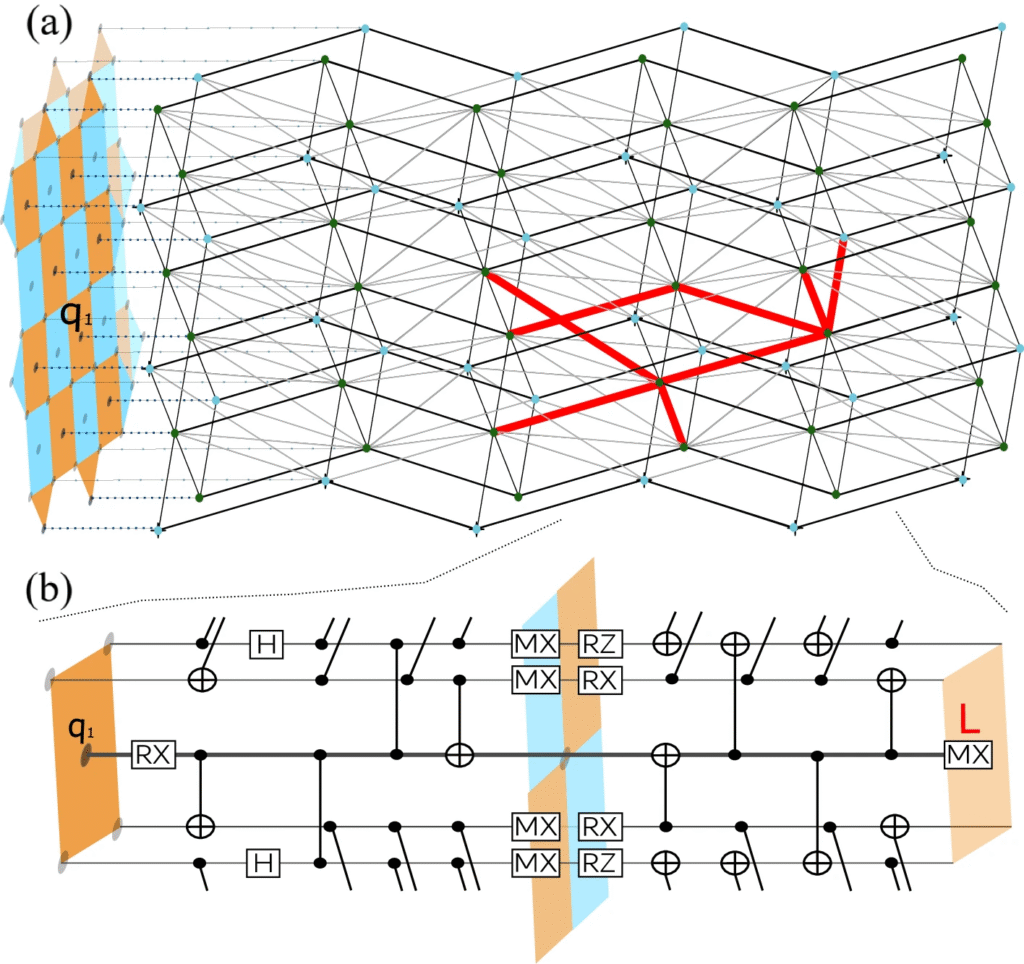

The LCD architecture, implemented on FPGA hardware, utilizes a coarse-grained parallel design to balance throughput with resource efficiency. It operates by grouping nearby qubit errors into clusters and resolving them in parallel, a method naturally suited for the surface code architecture used by many leading quantum hardware providers.

A primary technical differentiator of the LCD is its adaptivity engine. As a quantum computer operates, the decoder continuously updates its internal noise model in response to control signals. This allow the system to recognize and mitigate correlated errors, such as “leakage”—a damaging event where a qubit drifts out of its computational basis (∣0⟩ and ∣1⟩) into a higher excited state (∣2⟩). By adjusting “on the fly,” the decoder functions similarly to a GPS that recalculates routes based on changing road conditions.

The research demonstrates that adaptive decoding can reduce the physical qubit overhead required for fault tolerance by up to 75%. In a leakage-dominant noise model, the LCD achieved target logical performance with a code distance of d=17, whereas a non-adaptive decoder required d=33. Since physical qubits scale quadratically with code distance (d 2 ), this efficiency allows for a system roughly one-fourth the size of traditional designs.

The LCD technology forms the core of Riverlane’s Deltaflow QEC stack, which is already deployed with partners including Infleqtion, Oxford Quantum Circuits, Rigetti Computing, and Oak Ridge National Laboratory. Riverlane’s roadmap targets Deltaflow 3 in late 2026, which will introduce “streaming logic” to detect and correct errors continuously during logical operations, a prerequisite for million-qubit systems.

Read the full study in Nature Communications here and the official announcement here.

December 19, 2025