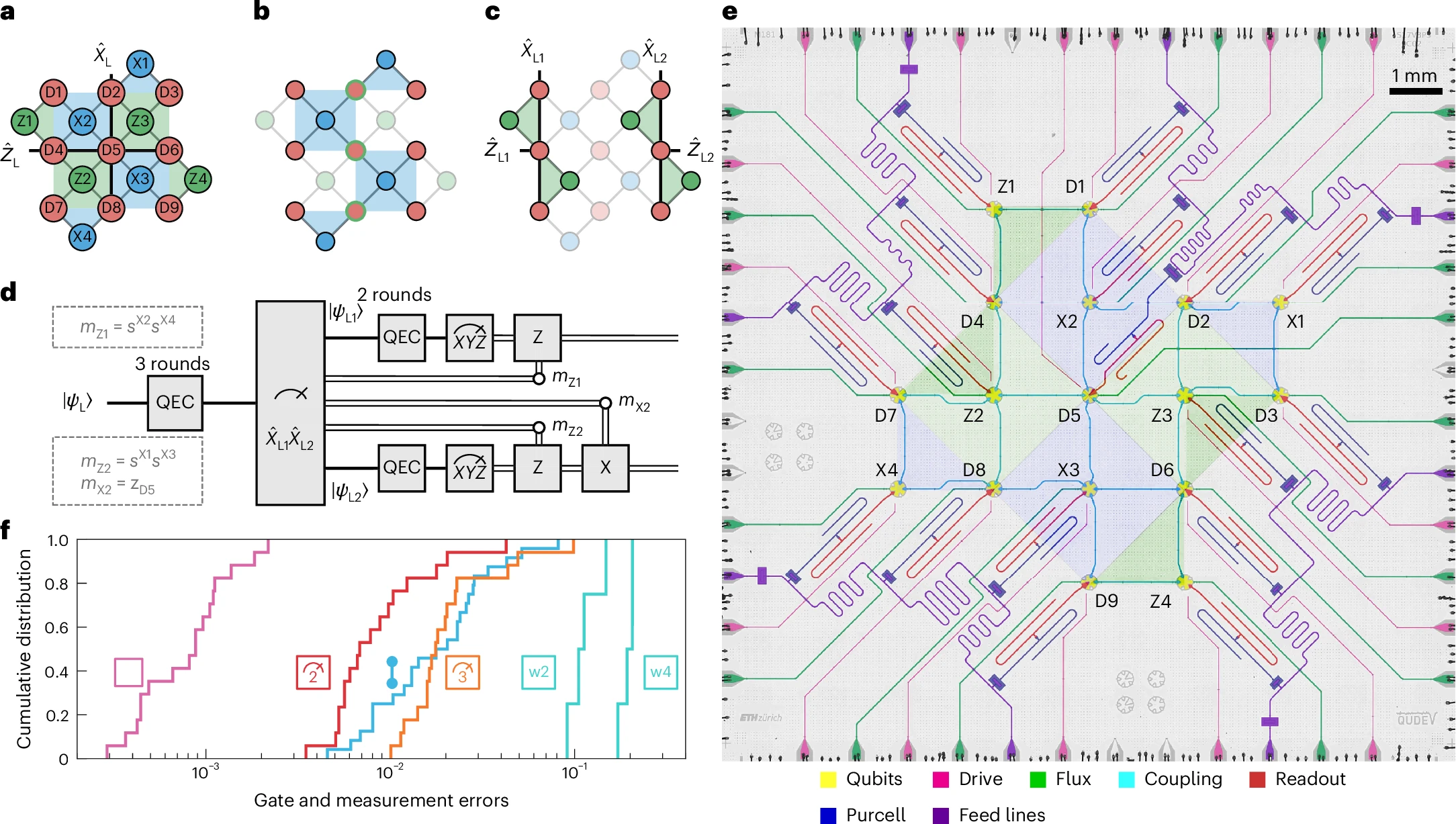

Researchers from the Paul Scherrer Institute (PSI) and ETH Zurich have demonstrated the execution of a logical quantum operation using lattice surgery on a 17-qubit superconducting processor. The experiment, published in Nature Physics, illustrates a method for entangling two logical qubits while maintaining active quantum error correction (QEC) protocols. The team utilized a rotated distance-three surface code architecture to perform a “split” operation, a fundamental building block for implementing logical gates like the controlled-NOT (CNOT) in planar qubit arrays with fixed local connectivity.

The technical architecture involved 17 flux-tunable transmon qubits arranged in a two-dimensional lattice. The system initially encoded a single logical qubit using nine data qubits and eight auxiliary qubits for stabilizer measurements. During operation, the researchers applied an X-type lattice split, which involved reading out a central column of three data qubits (D2, D5, D8) in the Z basis while halting X-type stabilizer measurements along the splitting boundary. This code deformation transformed the single surface-code qubit into two distinct logical degrees of freedom encoded as distance-three bit-flip repetition codes. Stabilizer measurements were performed in cycles of 1.66 microseconds, allowing the system to identify and correct bit-flip errors occurring during the surgery.

The results indicate that the fault-tolerant circuit achieved a measurable improvement in the ZZ logical two-qubit observable compared to an equivalent non-encoded (distance-one) circuit. While the current 17-qubit implementation is fault-tolerant specifically for bit-flip errors, the researchers noted that expanding the system to 41 physical qubits would enable simultaneous protection against phase-flip errors. This demonstration validates lattice surgery as a viable mechanism for performing entangling gates between logical qubits in architectures with constrained connectivity, providing a modular pathway for scaling superconducting quantum processors toward fault-tolerant algorithm execution.

Read the full technical paper in Nature Physics here and the background story from PSI here.

February 7, 2026

Leave A Comment